While the semiconductor industry has been facing the chip-shortage for about a year now, one major issue that has been lurking in the shadows for years but hasn’t got much consideration is debugging layout parasitics. To deal with the problem, Diakopto was founded on the recognition that parasitics are now a first-order problem. The semiconductor industry demands a radical change in methodology and tools to meet the challenge.

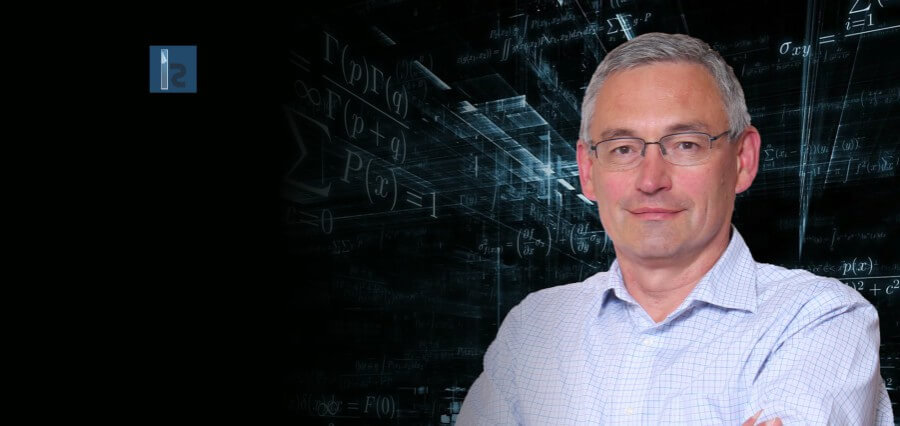

Committed to resolving this issue, Co-founder Maxim Ershov pioneered a new methodology that attacks the problem from the perspective of the engineers tasked with IC design and layout optimization. As the CEO and CTO of the company, he is driving the development of a new breed of EDA tools – easy to use, intuitive, orders of magnitude faster, visual, and providing actionable insights.

Let us have a rundown of their innovative approach.

The Overview

Expressing his view, Maxim states that the industry migration to advanced FinFET nodes (16nm and below) – coupled with the demand for higher speed and higher precision circuits – has led to a paradigm shift: parasitics from on-chip wires and interconnects are now more problematic than transistors. The increased complexity – more metal layers, thinner, narrower, proximity to each other – has driven an exponential rise in the number, magnitude, and severity of parasitics impacting on-chip performance, power, and time-to-market; at the same time, market windows are shrinking.

Maxim continues that existing EDA tools and methodologies have not adapted to this new reality, and because of this the industry has experienced a perfect storm. Engineers spend countless days and weeks trying to resolve numerous problems caused by layout parasitics. Most EDA tools treat parasitics analysis as a “black box,” delivering no insights into the causes of problems, forcing engineers to adopt a trial-and-error approach.

Diakopto is disrupting the industry by offering unique products to fill a void to end the frustrating and time-consuming debugging process. Its products are designed around a new approach to help engineers develop next generation chips more effectively and efficiently. The methodology is based on three principles:

1) Find the sources of major design problems to focus resources on the most critical issues that impact the overall circuit (and don’t spend time on insignificant issues).

2) Speed the analysis, so results come back significantly faster.

3) Provide visual context so engineers can see where problems occur and how they impact overall circuit performance.

And an overriding theme is to make the company’s solutions intuitive, easy, and enjoyable to use.

Best-in-Class

Diakopto’s first product, ParagonX™, was announced this year and is proving to fill the gap unmet by other approaches to debugging and design optimization. ParagonX delivers intelligence and insights that help designers explore and find solutions to fix problems and improve designs more quickly.

Maxim states that IC debugging and optimization time is reduced to minutes or hours by enabling engineers to focus effort on the most problematic parasitic elements (ignoring thousands, even billions of insignificant ones). He says, “ParagonX delivers a comprehensive set of rapid analyses integrated with visualization, which helps users analyze, visualize, and debug a broad range of problems caused by layout parasitics. The acceleration of the design process is aided by the capability to visualize parasitic effects over the layout.”

Why Diakopto?

Diakopto’s solutions have already been adopted by over 35 industry-leading customers, including some of the largest semiconductor companies, system OEMs, and hyper-scale data center corporations.

Maxim believes there are numerous reasons for the rapid adoption of the company’s products. With today’s design complexity and iterative nature of the design flow, designers and layout engineers need a tool to help them analyze and visualize RC effects to understand and debug circuits throughout the design process.

Before ParagonX, no such tool existed. ParagonX spots RC weaknesses in the circuit layout without requiring lengthy simulations. ParagonX provides IC design, CAD, and layout engineers an understanding of parasitic effects to more intelligently identify the main sources of circuit problems caused by interconnects and focus their efforts on resolving those that will yield the greatest benefits for the overall circuit. This results in fewer iterations during simulation because of the analyses and optimizations enabled by ParagonX at the design phase.

Sharing his insights, Maxim says, “ParagonX compliments existing design flows and doesn’t replace any existing tools. The disruption it is causing is that it enhances existing design processes, and for the first time, puts a targeted tool in the hands of those engineers tasked with parasitics debugging. Elevating their endeavors from a “whack-amole” approach to one that facilitates design optimization with insight as a key part of the process.”

The Pillars of Diakopto

Talking about the values of the organization, Maxim says, “As engineers and scientists focused on EDA, we are committed to helping engineers engaged in solving the increasingly critical and often frustrating problem of parasitics debugging.”

He adds, “Parasitics debugging is often viewed as dirty work, something that everyone knows is an enormous issue”, but points out that to date, there’s been no glamour in having to deal with it and no tools specifically designed to address this. “We are passionate about delivering solutions that elevate parasitics debugging, design verification, and optimization to their rightful place in the IC design process. We help accelerate time-to-tapeout – and even make dealing with parasitics an enjoyable endeavor for our customers,” asserts Maxim.

Helping Hand to the Design Community

Diakopto solutions are being welcomed by the IC design community it serves. For the first time, the parasitics debugging process empowers engineers to leverage their experience and intellect more highly to impact the quality of the overall design and make significant contributions to PPA.

Envisioning Future

As expected, Diakopto will continue to address the needs of IC design verification and optimization using the same methodology as embodied in ParagonX. The demand for additional solutions has driven Diakopto to expand its development team in 2021, with a highly experienced team of engineers and scientists. The company recently released a second product to early customers and plans additional product introductions in 2022.